Abstract

This article discusses non-isolated, trans-inverse, coupled inductor (CI)-based, soft-switching, high-gain DC-to-DC converter topology for renewable sources. The three-winding CI is utilized to achieve a high voltage gain with a reduced turns ratio. The energy associated with the magnetic components is recycled by the passive clamp circuit through diodes, and finally it pushes the output voltage to enhance the converter voltage gain. Besides, the soft switching performance of the clamping circuit occurs during the turn-off time of the controlled switch, thereby reducing the switching loss and the reverse recovery issue on the diodes. The proposed topology benefits from a reduced component count and enhances the output voltage gain. Furthermore, the topology performance analysis is carried out using PSIM simulation, and a 250W prototype using a dSPACE controller is analyzed with theoretical expressions.

Similar content being viewed by others

Introduction

Electric vehicles1 play a major role in creating a pollution-free environment by integrating the electric vehicle charging system with any one of the renewable energy sources, making it more efficient with zero emissions. In electric vehicle charging2 systems integrated with renewable energy sources, the converters must manage continuous input current, handle a wide range of voltage gain with a lower duty cycle, and achieve a high voltage conversion ratio using the fewest number of components possible. This article focuses on designing the most appropriate converters to meet the above attributes.

In3 conventional DC-to-DC converters, such as boost and boost-derived non-isolated converters, do not achieve high gain at a large duty cycle. A larger duty cycle keeps the switch on for a long duration and increases the stress on the switch and other components, which leads to poor converter performances. The aforementioned shortcomings in conventional-type DC-to-DC converters led to the introduction of CI topology. CI used in4 and5 achieves high voltage gain while maintaining a lower duty cycle. The CI redirects its primary winding voltages to other energy storage elements, and finally, it pushes to the load side through one of the diodes. Use of CI simplifies the process of achieving high voltage gain in a DC-to-DC converter.

Voltage-boosting techniques such as the voltage multiplier (VM), switched capacitor (SC), switched inductor (SI) and cascaded technique (CT) are used by6,7,8 along with the coupled inductor. This cuts down on the number of semiconductor components, which makes the converter a little more efficient. Yet, these topologies suffer from voltage spikes in switches caused by leakage inductance, which lowers gain and efficiency. The high voltage spike causes the switch to fail. To solve the issue, use an active or passive clamp circuit across the switch. In8, the passive clamp circuits across the switches resolve these voltage spikes. As shown in9,10,11, the passive clamps circuits help recycle the energy from the CI to the clamping capacitor. This lowers the voltage spikes to below the output voltage and makes the converter more efficient. Even at low output voltage12, the hard switching and reverse recovery issues in the DC-to-DC converter negatively impact the converter’s efficiency. Therefore, to address the major problem of switching loss, the converter circuits must operate under soft-switching conditions, either zero voltage switching (ZVS) or zero current switching (ZCS). In13, adding soft switching along with an active or passive clamp circuit improves the ability to reduce voltage spikes and lowers the problem of reverse recovery by slowing down the current that leaks out of the leakage inductance. From a high-gain perspective, the lack of an input inductor renders this converter topology unsuitable. The problem mentioned above is fixed in14 by adding an input inductor to the topology. This topology works under a ZVS turn-on to achieve high voltage gain with the same turn’s ratio at high operating frequency.

Instead of using active and passive clamp circuits, the topology15 employs an auxiliary switch to clamp the voltage spike from the switch to the clamping capacitor. The system does not achieve a wide voltage gain. On the other hand, the topology in16 operates under a ZCS turn-on with a passive clamp circuit and achieves high voltage gain with the help of VM. Another topology17 uses the same passive clamp circuit with VM to achieve high voltage gain with fewer components. However, the topology significantly reduces the input current ripple, despite its high turn ratio. Therefore, the large size of the CI makes the topology occupy more space in the electric vehicle charging system.

Despite using two windings in the coupled inductor, the aforementioned topologies do not achieve a wide range of voltage gain, as they require more semiconductor devices and incur switching losses. Therefore, the voltage gain of the previously presented converters are limited. In order to meet the needs, the topology shown in18 uses a three-winding CI with a very low turns ratio. This lowers the leakage current and helps semiconductor devices with the reverse recovery problem. Moreover, a high ripple in the input inductor limits the duty cycle to 0.49. Typically, one must operate a converter at a duty ratio of 0.5 to achieve high-gain output voltage conversion. To get around the duty cycle limitation in three-winding CI19, adds two symmetrical VM structures in the middle of the circuit. This structure not only gets around the duty cycle limitation but also makes the voltage gain wider. The topology presented in20 is an extended version of topology19. The system combines a three-winding CI with two VMs, and the semiconductors operate under ZVS to achieve a wide range of voltage gain with a shorter duty cycle and higher efficiency. To manage the two boosting stages, the system employs an additional two power switches and two clamping circuits, resulting in a high component count.

The active switched inductor technique is used in21 to cut down on the number of semiconductor components and increase the voltage gain. This leads to good results in two switches with a wide voltage gain. In22, another topology utilizes the active switched capacitor technique with two switches, which broadens the output voltage and increases the gain through parallel charging of the switching capacitor and series discharge of the CI, leading to effective outcomes. To resolve the use of two power switches for two boosting stages, the topology23 employs only one switch with a new voltage lift technique by adding the capacitor in series with the first boosting stage. Hence, the other boosting stage capacitor voltage reflects the CI output voltage; as a result, the converter’s voltage gain increases with the sum of two boosting stages. Because the source and the CI connection are in series, this topology is susceptible to high input current ripple. Using passive elements to clamp the voltages of the input inductor at both ends can lower the input current ripple, as suggested by24. This keeps the voltage across the inductor constant and lowers the current ripple, but the topology requires an extra amount of inductors and capacitors, which makes the circuit larger and more complex.

To avoid the circuit’s complexity25,26,27, introduces the new efficient method of trans-inverse-based CI, which achieves high voltage gain with a reduced turns ratio. In this topology, the CI’s secondary winding turn ratio inversely influences the converter’s voltage gain. Despite the increased turn ratio between the primary and secondary windings, maintaining a constant voltage across the inductor and reducing the current ripple results in a narrower converter’s voltage gain.

Based on the above detailed primary requirements of a high gain DC-to-DC converter, a trans-inverse topology is proposed to achieve a wide voltage gain at a lower turn ratio by using a lower number of component counts and controlling the semiconductor devices with the soft switching technique. The key benefits of the suggested converter are

-

Deliver a large voltage gain at a reduced turns ratio.

-

Narrow duty cycle enables a wide voltage gain.

-

Reduce the input current ripple.

-

Achieve a high gain with a low component count.

-

Soft switching—ZCS of the main switch.

The operating principle of the proposed topology in different modes of operation with the respective waveform is discussed in Sect. “Operating principle of proposed topology”. Section “Topology performance analysis in steady-state condition” discusses the performance analysis of the topology under steady-state conditions, considering voltage gain and stress on semiconductor devices. Section “Performance evaluation” tabulates and discusses the performance evaluation of the proposed converter in comparison with the existing topology. Section “Design specifications of the proposed converter” provides the component design specification, while Sect. “Simulation and experimental results” displays the simulation and experimental results. Section “Conclusion” presents the final summary of the findings.

Operating principle of proposed topology

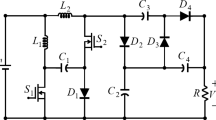

Figure 1 illustrates the proposed trans-inverse-based three-winding CI topology. The topology has two magnetic parts: a three-winding CI, which is shown by N1, N2, and N3; an input inductor (Lin); a single controlled switch (S); three diodes (D1, D2, Do) to make sure the current flows properly; and four capacitors: three temporary voltage storage capacitors (C1, C2, C3) and one output load capacitor (Co). The primary winding consists of one leakage inductance (Lk) and one magnetizing inductance (Lm).

The proposed converter achieves high voltage gain by setting the proper turn ratio of the secondary and tertiary windings with the help of capacitor C3 and diode D2, which enhance the boosting of the input voltage and finally drive out the boosting voltage to the output side. The formation of C2 and D1 in the clamping design relieves the maximum voltage stress across the gate-controlled switch, which has its own RDS-on. The series connection of the leakage inductance (Lk) with capacitors C1 and C2 ensures the soft switching action of the proposed topology, making the tertiary winding current sinusoidal and preventing the output diode from a reverse recovery dispute. To analyze the topology with different modes of operation in continuous conduction mode, the circuit is considered ideal with no loss components. Figure 2 displays the theoretical waveform of the proposed converter, followed by the various modes of operation at the different time intervals as listed below.

Mode—1[to – t1], Fig. 1 shows the controlled input to the semiconductor switching device (S), which includes the turn ON and turn OFF durations. During the turn-on duration to to t1 as shown in Fig. 3a, the input inductor (Lin) is energized; hence the inductor current rises linearly with a positive slope and diode D1 is in the OFF condition. Capacitor C1 and leakage inductance (Lk) are discharged to capacitor C2 through primary and secondary windings. Due to the discharge of capacitor C3, the diode Do transitions to the forward conduction state, while D2 transitions to the reverse blocking state, supporting both Co and the load. In this short duration, the magnetizing inductor Lm starts rising linearly under a positive slope. This mode continues until Lk discharges completely.

Mode–2[t1–t2], During the interval from t1 to t2 as shown in Fig. 3b the controlled power switch remains in the ON state, and the input inductor (Lin) continues to charge linearly. The leakage inductance (Lk) charges in the opposite direction. The capacitor C2 discharges the stored energy to C1 and to the primary winding of CI. Throughout the operation, the capacitors C1, C2 and leakage inductance (Lk) are connected in series to form the resonant tank and make the leakage inductance and CI current as a quasi-sine wave. But the diode D2 remains in the reverse blocking state due to the discharging of C3. At the end of this mode, the Do current reaches zero, thereby achieving the Low Reverse Recovery (LRR) condition. Equations (1) to (4) represent the derived resonant frequency and output voltage during this mode.

Mode–3[t2–t3], In Fig. 3c, the controlled power switch is turned OFF. Therefore, the current from the input inductor (Lin) and leakage inductor (Lk) flows through the clamp circuits D1 and C2, as well as the body diode of the controlled switch. This protects the power switch from the high voltage stress caused by the ZCS action. Consequently, the capacitor C2 starts charging. The current from the primary and secondary windings of CI reduces to zero at the end of this mode. This mode operates more quickly.

Mode–4[t3–t4], the power switch is still in the OFF state as shown in Fig. 3d. Capacitor C1 still charging, and the leakage inductance (Lk) current rises to a positive slope due to the secondary winding of CI. The input inductor (Lin) and the magnetizing inductor (Lm) are discharging linearly. The current from the secondary winding makes the diodes D2 and Do turn on and off respectively, while the capacitor C3 gets charged from the source and the load is supported by Co. At the end of this mode, the LRR condition turns the clamping circuit OFF as the diode D1 current reaches zero. The input inductor and capacitor C3 voltages are derived and shown in the Eqs. (5) to (7).

Mode–5[t4–t5], as the power switch is still in the OFF state, the previous state of leakage inductance (Lk) current remains unchanged. The capacitor C1 is discharging to C2 through the secondary winding of CI. While the input inductor Lin is continuously discharging, the source continues to charge the capacitor C3 through D2 and the tertiary winding of CI. The capacitor Co supports the load and keeps the diode Do in a reverse blocking state as shown in Fig. 3e. The power switch turns ON at the end of this mode.

Topology performance analysis in steady-state condition

Voltage step-up conversion

Apply the volt-second balance to the inductor during the switch ON and switch OFF instances, taking into account modes 2 and 4, to calculate the gain of the proposed converter. Using Eqs. 2, 3, 4, 5, 6, the volt-second balance relations are given below.

Based on equation the Eqs. (8) and (9), the following capacitor voltages are obtained,

By substituting the value of VC2 in VC1 (Eqs. (10) and (11)), the equation for VC1 is expressed in (12)

From Eqs. (6) and (7), the value of VC3 is expressed in Eq. (13)

Equation (14) projects the relationship between the input and output voltage gain of the proposed converter by substituting the values of VC1, VC2, and VC3 in VO.

The differences in leakage inductance current, as shown in Fig. 3a,b, negatively impact the output voltage gain in the above output equation. Therefore, the voltage gain of the proposed converter is simplified to Eq. (15).

The voltage gain of the proposed converter depends on duty cycle and CI’s secondary and tertiary winding turn ratios. Figure 4a depicts the variation of proposed topology voltage gain with respect to the variation of the control input at constant n3 = 0.8 for different cases of n2 (1.1, 1.2, 1.3, 1.4, 1.5). Similar figure is portrayed in Fig. 4b for different cases of n3 (0.8, 0.9, 1, 1.1, 1.2) at constant n2 = 1.2.

It is inferred from Fig. 4a, that the voltage gain varies when the turns ratio of n2 is selected between 1.1 to 1.5 and it is observed that the voltage gain is maximum for 1.1 ≤ n2 ≤ 1.2. Hence as the turns ratio of n2 decreases, the voltage gain reaches maximum value and therefore the suggested topology exhibits a trans-inverse characteristics. Extending the similar analysis to Fig. 4b, the turns ratio of n3 value is selected between 0.8 ≤ n3 ≤ 1. Based on the above range of values of n2 and n3 voltage gain of Eq. (15) is displayed in Fig. 5 at D = 0.5. Due to the trans-inverse characteristics, n2 is varied between 1.1 and 1.2 for the different cases of turns ratio of n3 (case 1: n3 = 0.8; case 2: n3 = 0.9 and case 3: n3 = 1). Consequently, the voltage gain of the suggested topology shown in Fig. 6 is achieved by varying the controlled input D by fixing the value of n2 = 1.2 and n3 = 1.

Stress on semiconductor devices

The maximum voltage stress across the switch, diodes D1, D2 and Do during one switching cycle is written as follows,

Using the Eqs. (16) to (19), the calculated diode voltages are very less compared to the output voltage of the converter and it proves that the passive clamping circuit of the switch works efficiently for the proposed converter.

By considering the output voltage as the base value, the normalized voltage stresses of the semiconductors are displayed in Fig. 7.

It is evident from Fig. 7 that the voltage stress of the switch and diodes are lower than the semiconductor devices reported in25 and16.

The typical calculated value of average current in inductor and diodes are given in Eqs. (20) to (22).

where, R is the load resistance of the converter. The normalized current stress of the devices are displayed in Fig. 8 by considering the input current as the base value. The normalized switch current shown in Fig. 8 is 1.5 p.u whereas, the normalized switch current reported in25 and16 is higher than 1.5 p.u and it is equal to 1.9 and 1.97 p.u respectively. Due to this, the corresponding diode D1 across the switch draws current around 1.8 p.u and it is lower than the diode currents reported in25 and16. The normalized output diode current of Do is very low whereas the diode D2 normalized current is equal to 1.8 p.u as it is connected between the secondary and tertiary winding of the coupled inductor. Hence the proposed topology normalized switch/diode currents are lower than the device currents reported in25 and16.

Performance evaluation

The advantages of the suggested converter are examined by comparing with the most recent converters as projected in Table 1. In order to compare the performance of the different converters, Fig. 9 shows the voltage gain with the parameters n2 = 1.2 and n3 = 1 for converters with three-winding CI topologies and n = n2 + n3 = 2.2 for converters with two-winding CI. In addition to having fewer components, it is clear that the suggested converter has a high voltage gain and lower voltage stress across the MOSFET for a control input of D = 0.5. As a result, conduction losses and cost can be greatly decreased by using low voltage rating MOSFETs with lower RDS-on values.

Figure 10a,b illustrate the voltage stress on the switch (S) and output diode (Do) for all topologies by taking the value of D = 0.5. The clamping action of C2 and D1 in the proposed converter effectively reduces the voltage stress on the switch. The voltage stress on the output diode is not beyond the output voltage of the converter. The wider voltage gain in a lower duty ratio is also one of the unique features of the proposed converter.

To illustrate the performance of the non-ideal mode of the converter, the non-ideal gain of the proposed converter is derived26 and shown below in Eq. (23).

where \({\text{R}}_{\text{eq}}={\text{R}}_{\text{L}}+{\text{DR}}_{{\text{Ds}}_{(\text{on})}}+{\text{R}}_{\text{c}1}+{\text{R}}_{\text{c}2}+{\text{R}}_{\text{c}3}+{\text{R}}_{\text{co}}+{\text{R}}_{\text{Lk}}+{\text{R}}_{\text{n}1}+{\text{R}}_{\text{n}2}+{\text{R}}_{\text{n}3}\)

And the parasitic parameters of the components/devices are given below.

(RL=15mΩ, RDS(on)=5.6mΩ, RC1=5mΩ, RC2=15mΩ, RC3=10mΩ, RCo=75mΩ, RLk=5mΩ, Rn1=12mΩ, Rn2=18mΩ, Rn3=12mΩ, VFD1=VFD2=VFDo=0.8V)

In Eq. (23), R can be approximated to R + Req, because R is very high. Hence the effect of parasitic elements are negligible and the non-ideal voltage gain coincides with the ideal voltage gain as observed in Fig. 11.

The sensitivity of the non-ideal voltage gain is tested with respect to forward voltage drop of diodes and RDS(on) of the controlled switch. The effect of variation of RDS(on) is negligible as it can be inferred from the Fig. 12a,b, whereas the effect of the forward voltage drop of the diodes is observed in Fig. 12c,d, but it is not dominant. Consequently the proposed converter is insensitive to parasitic variations.

Design specifications of the proposed converter

Table 2 presents, the design of the components. For D = 0.5, the voltage stress on the main switch/diode is significantly decreased, and the input inductor is designed with the value of D = 0.5 to handle the low input current ripple of 15%. Hence, the Eq. (24) is derived and projects the change in the ripple current.

The current ripple of the magnetizing inductance is calculated by using the expression (25) based on a 10% current ripple.

The maximum output voltage ripple on the load side is derived based on a 2% voltage ripple, and the expression of the output filter capacitor is shown in Eq. (26).

The remaining capacitors of the proposed topology (C1, C2, C3) are designed according to modes of operation as portrayed in Fig. 3, for achieving high voltage gain and presented in Eqs. (27) to (29).

Simulation and experimental results

The functionality of the proposed high gain trans-inverse topology is tested in PSIM with the following parameters: Vin = 25 V, fs = 50 kHz, D = 0.5 for the output power of 250W, output voltage = 450 V and load current = 0.55A. The magnetizing components, capacitive components and the semiconductor switching devices are indexed in Table 2.

The controlled input (VGS) of the switching device (S) with equal ON time and OFF time is shown in Fig. 13a. As per the Fig. 3, the inductor current with a ripple value of 0.6A is shown in Fig. 13b along with the leakage inductance current in Fig. 13c.

During the turn OFF condition of (S) shown in Fig. 14a, diode D1 conducts for a short duration with peak value of 25A as projected in Fig. 14b. The remaining diode currents (ID2 and ID3) are portrayed in Fig. 14c,d and it is interpreted that diode Do conducts during turn ON time of (S) while the diode D2 conducts during the turn OFF time. The magnitude of IDo and ID2 are less than 2A.

The charging and discharging of the capacitors C1, C2 and C3 are observed in Fig. 15 with ripple values of 15, 5 and 3% respectively.

The aforementioned simulation waveforms are obtained by operating the controlled switching device (S) under ZCS condition and the same is observed in Fig. 16. It is evident from the Fig. 16a,b that the switch current reaches zero before the falling edge of the gate pulse (VGS) and simultaneously the voltage of the switch increases gradually due to the clamping circuit. Consequently, the output voltage of the proposed topology reaches the steady state value of 450 V at 0.55A as portrayed in Fig. 17a,b respectively.

The prototype of the proposed high gain converter as shown in the Fig. 18, was constructed using MOSFET IPP076N15N5 and fast acting diodes MUR820. The controlled switch IPP076N15N5 is selected based on low voltage stress of about 40 V as inferred from Fig. 16b and driven by TLP350. The dSPACE controller-MicroLabbox is used to generate the gate pulse for IPP076N15N5 and the experimental results are captured using KEYSIGHT MSOX3014G scope with necessary current probe and voltage differential probe as portrayed in Fig. 18. The experimental results of Figs. 19, 20, 21, 22 are validated with the corresponding simulation results of Figs. 13, 14, 15, 16, 17.

The loss calculation27 is applied for the proposed converter to obtain the losses of all the components and the corresponding equations are shown in Table 3. Using Table. 3, the efficiency of the proposed converter at 250W is calculated and is equal to 96.5%. The percentage loss distribution is shown in Fig. 23. From Fig. 23 it is observed that the effect of the losses is minimum.

The prototype was validated in different power range and at full load an efficiency of 96.5% is achieved and shown in Fig. 24. The results project the feasibility of the proposed topology in the field of electric vehicles.

Conclusion

This article presents a trans-inverse three-winding CI-based high-gain DC-to-DC converter. The proposed topology achieves high voltage gain by reducing the CI turns ratio and total component count. The clamping circuit performs the ZCS action and lowers the voltage stress during the switch turn-off time. Compared with the other topologies, the proposed topology achieves high voltage gain at a lower turn’s ratio and at a low component count by turning off the main switch using ZCS. The proposed topology is simulated, and the results are validated for the 250W, 450 V prototype under various power conditions using the dSPACE controller. The proposed topology reaches a high efficiency of 96.7% at a power output of 225W.

Data availability

The datasets used and/or analysed during the current study are available in the manuscript.

References

Kouro, S. et al. Grid-connected photovoltaic systems: An overview of recent research and emerging PV converter technology. IEEE Ind. Electron. Mag. https://doi.org/10.1109/MIE.2014.2376976 (2015).

Teng, F., Ding, Z., Zechun, Hu. & Sarikprueck, P. Technical review on advanced approaches for electric vehicle charging demand management, part I: applications in electric power market and renewable energy integration. IEEE Trans. Ind. Electron. https://doi.org/10.1109/TIA.2020.2993991 (2020).

Forouzesh, M. et al. Step-up DC–DC converters: A comprehensive review of voltage-boosting techniques, topologies, and applications. IEEE Trans. Power Electron. https://doi.org/10.1109/TPEL.2017.2652318 (2017).

Schiavon, G. L., Agostini, E. & Nascimento, C. B. Quasi-resonant single-switch high-voltage-gain DC-DC converter with coupled inductor and voltage multiplier cell. Energies https://doi.org/10.3390/en16093874 (2023).

Hajiabadi, M. K., Eshkevari, A. L. & Abdoli, I. A high step-up coupled-inductor-based dc-dc converter with a wide duty cycle range and improved gain-to-element ratio. IET Power Electron. https://doi.org/10.1049/pel2.12602 (2023).

Imanlou, A., Najmi, E. S. & Babaei, E. A new high voltage gain DC-DC converter based on active switched-inductor technique. Int. J. Circ. Theor. Appl. https://doi.org/10.1002/cta.3768 (2024).

Burle Tulasi Rao and Dipankar De. Effective leakage energy recycling in high gain DC-DC converter with coupled inductor, IEEE Transactions on circuits and systems—II: Express Briefs. https://doi.org/10.1109/TCSII.2022.3159867. (2022).

Hasanpour, S., Siwakoti, Y. & Blaabjerg, F. Hybrid cascaded high step-up DC/DC converter with continuous input current for renewable energy applications. IET Power Electron. https://doi.org/10.1049/iet-pel.2020.0544 (2020).

Hasanpour, S. et al. New semiquadratic high step-up DC/DC converter for renewable energy applications. IEEE Trans. Power Electron. https://doi.org/10.1109/TPEL.2020.2999402 (2021).

Hasanpour, S., Siwakoti, Y., Mostaan, A. & Blaabjerg, F. New Single-Switch quadratic boost DC/DC converter with Low voltage stress for renewable energy applications. IET Power Electron. https://doi.org/10.1049/iet-pel.2020.0580 (2021).

Sedaghati, F. & Pourjafar, S. Analysis and implementation of a boost DC–DC converter with high voltage gain and continuous input current. IET Power Electron. https://doi.org/10.1049/iet-pel.2019.0973 (2019).

Lish, M. H., Ebrahimi, R. & Kojabadi, H. M. Novel high gain DC–DC converter based on coupled inductor and diode capacitor techniques with leakage inductance effects. IET Power Electron. https://doi.org/10.1049/iet-pel.2020.0117 (2020).

Reddy, D. V. S. & Thangavel, S. Zero voltage switching high step-up boost converter with coupled inductor for renewable energy applications. Int. J. Circ. Theor. Appl. https://doi.org/10.1002/cta.3382 (2022).

Kalahasthi, R. B., Ramteke, M. R. & Suryawanshi, H. M. A high-gain low-ripple DC–DC converter for micro-grid applications. Int. J. Circ. Theor. Appl. https://doi.org/10.1002/cta.3466 (2022).

Mirzaee, A. Coupled inductor-based high voltage gain DC–DC converter for renewable energy applications. IEEE Trans. Power Electron. https://doi.org/10.1109/TPEL.2019.2956098 (2020).

Kalahasthi, R. B., Ramteke, M. R. & Suryawanshi, H. M. A single-switch high-gain DC–DC converter for photovoltaic applications. Int. J. Circ. Theor. Appl. https://doi.org/10.1002/cta.3205 (2021).

Hasanpour, S. New step-up DC/DC converter with ripple-free input current. IEEE Trans. on Power Electron. https://doi.org/10.1109/TPEL.2023.3336005 (2024).

Hajilou, M. & Farzanehfard, H. Soft-switched high step-up quasi-Z-source converter with low switch voltage stress. IEEE Trans. Ind. Electron. https://doi.org/10.1109/TIE.2024.3383032 (2024).

Pereira, A. V. C., Cavalcanti, M. C. & Azevedo, G. M. A novel single-switch high step-up DC–DC converter with three-winding coupled inductor. Energies https://doi.org/10.3390/en14196288 (2021).

Burle tulasi rao and Dipankar De, A coupled inductor-based high-gain ZVS DC–DC converter with reduced voltage stresses, IEEE Transactions on Power Electronics, https://doi.org/10.1109/TPEL.2023.3310577. (2023).

Li, C., Li, H. & Wang, N. A full soft-switching high step-up DC/DC converter with active switched inductor and three-winding coupled inductor. IEEE Trans. Power Electron. https://doi.org/10.1109/TPEL.2023.3287974 (2023).

Zhang, X., Sun, L. & Guan, Y. Novel high step-up soft-switching DC–DC converter based on switched capacitor and coupled inductor. IEEE Trans. Power Electron. https://doi.org/10.1109/TPEL.2020.2972583 (2020).

Vesali, M. A new three winding coupled inductors high step-up DC–DC converter with low input current ripple. IET Power Electron. https://doi.org/10.1049/pel2.12522 (2023).

Yao, T. & Kou, J. Zero input current ripple DC-DC converter with high step-up and soft-switching characteristics. IEEE Trans. Ind. Appl. https://doi.org/10.1109/TIA.2023.3293491 (2024).

Hasanpour, S., Nouri, T. & Blaabjerg, F. High step-up SEPIC-based trans-inverse DC–DC converter with quasi-resonance operation for renewable energy applications. IEEE Trans. Ind. Electron. https://doi.org/10.1109/TIE.2022.3150103 (2023).

Kumar, M. & Gupta, R. Stability and sensitivity analysis of uniformly sampled dc-dc converter with circuit parasitics. IEEE Trans. Circuits Syst. I Regular Pap. https://doi.org/10.1109/TCSI.2016.2598834 (2016).

Hasanpour, S. et al. Analysis of a new soft-switched step-up trans-inverse DC/DC converter based on three-winding coupled-inductor. IEEE Trans. Power Electron. https://doi.org/10.1109/TPEL.2021.3103978 (2021).

Funding

Open access funding provided by Vellore Institute of Technology.

Author information

Authors and Affiliations

Contributions

Sriramkumar Venkatesan, the first author, has carried out the design of a novel soft-switched DC-DC converter using a three-winding coupled inductor and performed the experiments in the laboratory under the corresponding author’s guidance, Nandagopal Arun. The corresponding author is responsible for the development of this journal manuscript with the support of his Ph.D. student, Mr. Sriramkumar Venkatesan.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Venkatesan, S., Nandagopal, A. Soft switched high gain trans inverse DC-DC converter based on three winding coupled inductor for renewable energy applications. Sci Rep 15, 9051 (2025). https://doi.org/10.1038/s41598-025-92967-w

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-025-92967-w