Abstract

In this study, we propose a novel compensation scheme that utilizes variable reset voltage (VRV) to mitigate the flicker phenomenon observed in low temperature poly-Si and oxide (LTPO) active-matrix organic light emitting diode (AMOLED) displays at low frequencies. We have experimentally demonstrated that the flicker caused by luminance fluctuations at low frequencies is the result of interactions between the slow transient de-trapping of the oxide thin film transistor (TFT) and hysteresis of the driving TFT (D-TFT). Although slow transient de-trapping of the oxide TFT is difficult to be compensated, we have demonstrated that D-TFT hysteresis can be modulated by adjusting the gate in panel (GIP) timing and reset voltage. Accordingly, the luminance amplitude component at 1 Hz was significantly reduced from 0.201 cd/m2 to 0.093 cd/m2 by applying sequentially modulated VRV within the skip frame where image data were not updated. Consequently, the flicker phenomenon was improved at low driving frequencies below 10 Hz.

Similar content being viewed by others

Introduction

Mobile and portable devices are becoming increasingly essential parts of our daily lives, and there has been a growing emphasis on minimizing their power consumption owing to the dependency on batteries. For this purpose, variable refresh rate (VRR) is applied to active-matrix organic light-emitting diode (AMOLED) displays1,2, in which different refresh rates are used according to the display scenario3,4,5. For instance, a high refresh rate is used for scenarios such as watching videos or playing games to enhance moving picture quality6,7, whereas a low refresh rate is applied to static screens to lower the power consumption of the source driver integrated circuit (IC), which can dramatically reduce the overall power use.

In VRR driving, the luminance gradually changes in each time frame during low-frequency driving, leading to the flicker phenomenon8,9,10. In particular, the lower the frequency of these luminance changes, the easier it is for the human eye to perceive flickering11,12,13,14. Therefore, luminance fluctuations within the refresh rate range of 1–20 Hz are more noticeable to the human eye and can induce eye fatigue more easily than rapid luminance changes within the refresh rate range of 60–120 Hz refresh rates15.

Such flickering has been primarily attributed to the leakage current at the gate node of low-temperature poly-Si (LTPS)-based driving thin-film transistors (D-TFTs)16,17. Therefore, various studies have been conducted to utilize low-temperature poly-Si and oxide (LTPO) pixel structures using indium gallium zinc oxide (IGZO) channels with low-leakage current characteristics18,19,20,21,22,23,24,25. To mitigate the flicker issue, oxide TFTs with lower leakage current characteristics are connected to the D-TFT gate. However, the luminance continues to increase during skip frames where image data are not updated. Thus, it is suspected that factors other than the leakage current may contribute to this phenomenon. However, no clear interpretation or solution has been presented, and it is necessary to identify and solve the causes of the flickering phenomenon at low frequencies.

In this study, we analyze the mechanism of the low-frequency flicker phenomenon and present a novel driving method to minimize it. The cause of the flicker was investigated by observing the luminance waveforms while varying the driving voltage and timing. The compensation scheme in this study was verified to improve the flickering by applying a variable reset voltage (VRV) within the skip frame, which was measured on actual panels.

Operating principle of the LTPO panel

Figure 1 illustrates the concept of the refresh rate control, where the gate signal was set at 120 Hz. Using this concept, various refresh rates could be implemented by adjusting the number of skip frames. For instance, when playing a video, the number of skip frames was set to zero with a driving frequency of 120 Hz (Fig. 1a), whereas for static images such as text on the website, the number of skip frames was set to 11 with a driving frequency of 10 Hz (Fig. 1b). In the always-on display (AoD) mode, the number of skip frames increased to 119, allowing a significant power consumption reduction with a driving frequency as low as 1 Hz (Fig. 1c).

Concept of variable refresh rate (VRR); the number of skip frames varies depending on the operating frequency: (a) no skip frames at 120 Hz, (b) 11 skip frames per 12 frames at 10 Hz, and (c) 119 skip frames per 120 frames at 1 Hz. Figure was created based on free-license images and further processed using Microsoft PowerPoint (Microsoft 365, https://www.microsoft.com/powerpoint).

As shown in Fig. 2a, the gate in panel (GIP) block consists of five shift registers, and the link region is composed of the voltage lines. The S3 GIP block is designed with a 1-row and dual-feeding structure to enable VDATA sampling during 1-horizontal (1 H) time. In contrast, the EM, S1, S2, and S4 GIP blocks adopt a 2-row sharing and single-feeding structure to minimize the bezel size. Furthermore, the voltage lines in the link region are designed with a mesh routing structure that connects to all pixels. Figure 2b depicts the schematics of the LTPO AMOLED pixel circuit configured as 8T1C. In this circuit, T1 and T2, which are connected to the D-TFT gate node, are oxide TFTs, whereas the D-TFTs and T3–T7 are p-channel LTPS TFTs. Figure 2c illustrates the GIP signal control method within the pixel circuit, detailing the operations at each step. The driving voltages used in the evaluation are listed in Table 1. Here, VDD and VSS are the supply voltages and VGH and VGL are the high- and low-gate voltages, respectively. where VINT is the initial voltage, VRST is the reset voltage, and VDATA is the data voltage. The operating principles are described in detail as follows:

N4 initial

When the emission (EM) switch (SW) is turned off, the current flowing through the OLED disappears, and it does not emit light. Subsequently, when the S4 SW is turned on, the OLED anode node (N4) is initialized with the VINT voltage passing through T5 to prevent the OLED from emitting light owing to residual charges. In addition, a high VRST voltage is applied to the D-TFT source node (N1) through T4 to reduce the hysteresis effect in the next frame VDATA sampling caused by the previous frame VDATA26,27,28,29,30,31.

N2 initial

When S2 is turned on, the D-TFT gate node (N2) is initialized with the VINT voltage through T2. This initializes the previous frame VDATA.

N3 initial

When S1 and S2 are turned on, the D-TFT drain node (N3) is initialized with the VINT voltage through T1 and T2.

VDATA sampling

When S1 and S3 are turned on, VDATA is charged to the D-TFT gate node (N2) through T1 and T3. The voltage charged at the D-TFT gate node can be expressed by Eq. (1), where VG is the gate voltage of the D-TFT, and VTH is the threshold voltage of the D-TFT.

N1 reset

When S4 is turned on, a high VRST voltage is applied to the D-TFT source node (N1) through T4. This reduces the difference in the VTH change of the D-TFT caused by the hysteresis before the emission of the refresh and skip frames.

Emission

When the EM SW is turned on, the D-TFT current can be expressed using Eq. (3), which is based on Eqs. (1) and (2), where VS is the source voltage of the D-TFT, µ is the carrier mobility, COX is the gate oxide capacitance per unit area, and W and L are the channel width and channel length, respectively. VSG is the source-gate voltage of the D-TFT.

Results and discussion

Measurement

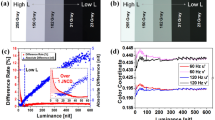

For the measurements, 6.5” AMOLED displays with quad high-definition (QHD) resolution and 8T1C compensation pixel structures were used. Optical measurements were performed using a KONICA MINOLTA CA-427, and the sampling rate of the measurement was set to 3 k/s. Measurements were conducted at the center of the panel using a 100 cd/m2 solid pattern. The normalized luminance was moving-averaged, equivalent to a single frame at 120 Hz, which was as effective as a low-pass filter. A moving average was used to filter out high-frequency elements that cause unnecessary disturbances when analyzing luminance trends within a frame. In Fig. 3a, it can be observed that the luminance gradually increases in the skip frames at both 1 and 10 Hz. This indicates that a severe flickering phenomenon is evident in a user environment that requires low-frequency driving, as shown in Fig. 3b. At 1 Hz, the number of skip frames is larger than that at 10 Hz, leading to a more severe flickering phenomenon. To determine the main cause of the increase in luminance during low-frequency driving, two evaluations were conducted.

First, to evaluate the impact of oxide TFTs, the GIP timing of oxide TFTs was not toggled in the skip frame, and the reset times for the refresh and skip frames were kept identical, as shown in Fig. 4a. The luminance waveform in Fig. 4c shows a gradual increase in luminance, indicating that the brightness is not saturated but continues to increase over a long-term period. Second, to evaluate the impact of D-TFTs, the GIP timing was set identically for the refresh and skip frames, but the reset times were different, as shown in Fig. 4(b). In this case, the refresh occurred even during the skip frame. The luminance waveform in Fig. 4d shows that the luminance rapidly decreases and saturates within a short period. The bias stress duration of the reset time in the skip frame (TRST_B) is longer than that in the refresh frame (TRST_A). This causes a stronger hysteresis effect in the D-TFT during the skip frame. Therefore, at the transition from the refresh frame to the skip frame, |VTH| increases and luminance decreases. However, in the latter part of the skip frames, where there is no difference in bias stress duration, this effect disappears.

Thus, it is determined that the impact of oxide TFTs is relatively long term, whereas that of D-TFT hysteresis is short term. Consequently, the increase in luminance caused by the oxide TFTs becomes more pronounced during low-frequency driving.

Slow transient de-trapping of oxide TFTs

We conducted an evaluation for the impact of leakage current in the drain-to-source direction of the oxide TFT by varying VINT and analyzing the luminance waveforms. As shown in Fig. 5, even when VINT is lowered to enhance the effect of leakage current, the luminance waveform remains unchanged, indicating that the impact of leakage current is minor. Therefore, the long-term luminance variation is interpreted as a result of persistent de-trapping rather than leakage current.

Figure 6a illustrates the mechanism by which the luminance increases due to oxide TFTs. When oxide TFTs are turned on during the refresh frame and then turned off, the trapped carriers accumulated in the channel are de-trapped towards the source and drain nodes, which lowers the potential at these nodes. Electrons are initially captured rapidly in shallow traps, but some transition to deep traps, leading to de-trapping that can persist for several seconds depending on various factors, including trap states and interface quality resulting from impurities or defects during the manufacturing process32,33,34,35. This slow transient de-trapping leads to a gradual decrease in the potential at the D-TFT gate node during the skip frame, causing an increase in the OLED current (IOLED), and consequently, an increase in luminance. Figures 6b and c show the SmartSpice simulation results, indicating that the IOLED continues to increase during the skip frame owing to the lowered potential at N2, regardless of whether the driving frequency is at 10 Hz–1 Hz. Thus, the phenomenon of increase in luminance in low-frequency driving aligns with the slow transient de-trapping phenomenon of oxide TFTs.

Hysteresis of D-TFTs

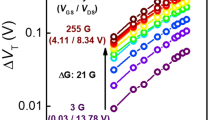

To investigate the D-TFT hysteresis effect, evaluations were conducted using various reset timings and voltages. For the first evaluation, we fixed TRST_A at 12 H time and varied TRST_B. We analyzed the luminance waveforms by adjusting the S4 gate signal. Figure 7a shows the adjustment of the reset time applied to the skip frame at three conditions: 52, 32, and 6 H. Figure 7c shows the peak-to-peak luminance variation during a single frame at 10 Hz when TRST_B is set to 52, 32, and 6 H. The longer the TRST_B is, the stronger the D-TFT hysteresis effect in the skip frame, leading to a decrease in luminance owing to the increase in |VTH|. In this test, both the reset voltages for the refresh frame (VRST_A) and skip frame (VRST_B) were 5.5 V. Because the peak-to-peak luminance variation is zero at a TRST_B of 40 H, it can be considered the optimal point for TRST_B.

For the second evaluation, VRST_A was fixed at 5.5 V and VRST_B was varied to observe the luminance waveforms. Figure 7b shows the adjustment of the reset voltage applied to the skip frame at three conditions: 5.8, 5.5, and 5.2 V. Figure 7d shows the peak-to-peak luminance variation during a single frame at 10 Hz when VRST_B is set to 5.8 V, 5.5 V, and 5.2 V. Similar to the results of the first evaluation regarding reset timing, the higher VRST_B is, the stronger the D-TFT hysteresis effect becomes in the skip frame, resulting in a decrease in luminance as |VTH| increases. In this test, TRST_A and TRST_B were set to 12 and 32 H, respectively. The peak-to-peak luminance variation is 0 at a VRST_B of 5.6 V, which can be considered the optimal point for VRST_B.

D. Improvement of Flicker with the VRV Compensation Scheme.

From the analysis of low-frequency luminance waveforms based on different reset timings and voltages, it was confirmed that the flicker phenomenon at 10 Hz can be improved by suppressing the increase in luminance due to the slow transient de-trapping of oxide TFTs by controlling the reset timing or voltage during skip frames. However, the hysteresis effect of the D-TFT is short. Therefore, its impact on luminance depends on the driving frequency. For instance, optimizing VRST_B for 10 Hz driving using 11 skip frames improves 10 Hz flicker, but 1 Hz driving using 119 skip frames still causes large luminance fluctuations owing to the slow transient de-trapping of oxide TFTs. Figures 8a and b show the 10 Hz and 1 Hz luminance waveforms, respectively, when an optimized VRST_B is applied for 10 Hz driving. Applying this VRST_B at 1 Hz causes a strong increase in luminance and similarly results in serious flickering.

To improve this, we first tried to compensate for the increase in luminance by extending the reset time applied in the latter part of the 1 Hz skip frame (12th − 119th ), but the S4 on-timing margin during the EM off state of the skip frame was insufficient. Accordingly, a strategy to adjust the reset voltage applied in the latter part of the 1 Hz skip frame (12th − 119th ) was adopted. Figure 9 shows the concept of VRV, where VRST_C is additionally introduced for voltage-compensated driving. The frame sync signal is counted to set the number of the skip frame from which VRST starts changing, and the frame counter is reset at every vertical synchronization (Vsync) cycle. The variable VRST is adjusted by modifying the bias of the low-dropout (LDO) regulator, which is connected to a digital-to-analog converter (DAC). This allows the voltage to be controlled according to the input lookup table (LUT) digital code. After optimizing VRST_B to offset the increase in luminance during 10 Hz driving, a higher VRST_C voltage is applied from the 12th skip frame to reduce the 1 Hz increase in luminance. As skip frames after the 12th cycle are only used at driving frequencies below 10 Hz, they have no impact on driving between 120 Hz and 10 Hz and can only suppress the increase in luminance at lower driving frequencies, where the number of skip frames significantly increases when driving below 10 Hz.

Figure 10 shows the luminance waveforms and frequency response characteristics when the new driving scheme with VRV is applied. Figure 10a shows the reference luminance waveform at 1 Hz when an optimized VRST_B for 10 Hz driving is applied. Figure 10b shows the 1 Hz luminance waveform when VRST_C, which is 25 mV higher than VRST_B, is applied after 100 ms, representing a single VRV. Although the increase in luminance was improved compared with the reference luminance waveform, the increase in luminance component is still observed in the latter half of the skip frame. Figure 10c shows the 1 Hz luminance waveform when VRST_C is applied after 100 ms, and VRST_D, which is 25 mV higher than VRST_C, is applied after 550 ms, representing a dual VRV. It was confirmed that the flicker characteristics significantly improved compared to the reference luminance waveform. Figure 10d shows the results of examining the luminance amplitude through the Fourier transformation of each luminance waveform. When VRST_C and VRST_D are applied, the frequency components in the range of 1–6 Hz are reduced to less than half of the reference.

Conclusion

In this study, we propose a novel scheme of applying VRV to improve the flickering phenomenon at low frequencies in LTPO AMOLED displays. Despite using oxide TFTs with low leakage current characteristics as switching TFT in LTPO AMOLED displays, problems exist for low-frequency driving. This is because the luminance continuously increases in skip frames owing to the slow transient de-trapping of oxide TFTs, which is challenging to compensate for. In our proposed scheme, as skip frames accumulate, the D-TFT hysteresis progressively increases to compensate for the rising luminance component, thereby improving the flicker. By employing two voltages, VRST_C and VRST_D, the luminance amplitude component at 1 Hz reduced from 0.201 cd/m2 to 0.093 cd/m2. The luminance amplitude components were reduced to less than half not only at the frequency of 1 Hz but also for other frequencies below 6 Hz, confirming a significant improvement in flickering. Depending on the characteristics of the oxide TFTs, applying additional voltages, such as VRST_E and VRST_F, at the desired skip frame positions will greatly assist in compensating the flicker characteristics at any driving frequency, thus significantly improving the display quality.

Data availability

All data analysed during this study are included in this published article. The raw data used are available from the corresponding author upon request.

References

Hong, S. et al. Development of commercial flexible AMOLEDs. SID Symp. Dig. Tech. Pap. 45 (1), 334–337. https://doi.org/10.1002/j.2168-0159.2014.tb00090.x (2014).

Na, S. H. et al. Enhancement of picture quality on ultra-low brightness by optimizing the electrical potential required for OLED charging in the AMOLED displays. J. Inf. Disp. 22 (4), 275–284. https://doi.org/10.1080/15980316.2021.1923581 (2021).

Yonebayashi, R. et al. High refresh rate and low power consumption AMOLED panel using top-gate n-oxide and p-LTPS TFTs. J. Soc. Inf. Disp., 28 (4), 350–359. https://doi.org/10.1002/jsid.888 (2020).

Oh, D. et al. Low frequency driving display to reduce logic power in liquid crystal display. SID Symp. Dig. Tech. Pap. 45 (1), 1199–1202. https://doi.org/10.1002/j.2168-0159.2014.tb00312.x (2014).

Kim, L. J. et al. Image quality enhancement in variable refresh rate AMOLED displays using a variable initial voltage compensation scheme. Sci. Rep. 12 (1), 5977. https://doi.org/10.1038/s41598-022-09892-5 (2022).

Kurita, T. Moving picture quality improvement for hold-type AM-LCDs. SID Symp. Dig. Tech. Pap. 32 (1), 986–989. https://doi.org/10.1889/1.1832037 (2001).

Kim, S. et al. A novel De-Mux and 120Hz driving technology for high resolution OLED displays. SID Symp. Dig. Tech. Pap. 49 (1), 540–542. https://doi.org/10.1002/sdtp.12460 (2018).

Moon, K. C., Wang, J., Gai, C. L., Li, J. F. & Park, K. Improving flicker of low-refresh-rate driven active-matrix organic light-emitting diode display. IEEE Access 10, 83705–83710. https://doi.org/10.1109/ACCESS.2022.3197171 (2022).

Kim, J. C. et al. LTPO driving technology for the next generation. In Proc. 28th Int. Workshop Active-Matrix Flatpanel Displays and Devices (AM-FPD), 144–146. (2021).

Chang, T. K., Lin, C. W. & Chang, S. LTPO TFT technology for AMOLEDs. SID Symp. Dig. Tech. Pap. 50 (1), 545–548. https://doi.org/10.1002/sdtp.12978 (2019).

Kim, H. et al. Effect of brightness and size on display flicker perception: comparison with flicker indices. J. Electron. Imaging. 36, 1–6. https://doi.org/10.2352/EI.2024.36.11.HVEI-235 (2024).

Kelly, D. H. Visual responses to time-dependent stimuli.* I. Amplitude sensitivity measurements. J. Opt. Soc. Am. 51 (4), 422–429. https://doi.org/10.1364/JOSA.51.000422 (1961).

Landis, C. Determinants of the critical flicker-fusion threshold. Physiol. Rev. 34 (2), 259–286. https://doi.org/10.1152/physrev.1954.34.2.259 (1954).

Chung, U. J. et al. Manufacturing technology of LTPO TFT. SID Symp. Dig. Tech. Pap. 51 (1), 192–195. https://doi.org/10.1002/sdtp.13835 (2020).

Kim, M. Assessment of the effect on the human body of the flicker of OLED displays of smartphones. J. Inf. Disp. 22 (4), 269–274. https://doi.org/10.1080/15980316.2021.1950854 (2021).

Lee, P. T., Lin, Y. S. & Lin, C. L. Compensation pixel circuit based on LTPS TFTs to improve effect of leakage current for AMOLED displays with low frame rate. In Proc. 27th Int. Workshop Active-Matrix Flatpanel Displays and Devices (AM-FPD), 107–110. (2021).

Lin, C. L. et al. Compensation pixel circuit to improve image quality for mobile AMOLED displays. IEEE J. Solid-State Circuits. 54 (2), 489–500. https://doi.org/10.1109/JSSC.2018.2881922 (2019).

Luo, H. et al. Complementary LTPO technology, pixel circuits and integrated gate drivers for AMOLED displays supporting variable refresh rates. SID Symp. Dig. Tech. Pap. 51 (1), 351–354. https://doi.org/10.1002/sdtp.13876 (2020).

Byeon, G. et al. Recent progress in the development of backplane thin film transistors for information displays. J. Inf. Disp. 24 (3), 159–168. https://doi.org/10.1080/15980316.2023.2219030 (2023).

Jeong, H. et al. Long life-time amorphous-InGaZnO TFT-based shift register using a reset clock signal. IEEE Electron. Device Lett. 35 (8), 844–846. https://doi.org/10.1109/LED.2014.2329933 (2014).

Mo, Y. G. et al. Amorphous-oxide TFT backplane for large‐sized AMOLED TVs. J. Soc. Inf. Disp. 19 (1), 16–20. https://doi.org/10.1889/JSID19.1.16 (2011).

Kim, T., Kim, Y., Ahn, J. & Kim, E. K. Enhancement of InGaZnO thin-film transistors by contact barrier modulation using oxygen defects. ACS Appl. Electron. Mater. 5 (7), 3772–3779. https://doi.org/10.1021/acsaelm.3c00508 (2023).

Kim, M. J. et al. Control of interfacial defect states in the flexible InGaZnO thin film transistor with a 6FDA-MDA gate insulator by using an Al2O3 interlayer. ACS Appl. Electron. Mater. 6 (2), 1151–1160. https://doi.org/10.1021/acsaelm.3c01554 (2024).

Ji, S. B. et al. Field-effect mobility extraction of solution-processed InGaZnO thin-film transistors considering dielectric dispersion behavior of AlOx gate insulator. ACS Appl. Electron. Mater. 5 (2), 1035–1040. https://doi.org/10.1021/acsaelm.2c01541 (2023).

Sun, X. et al. High performance indium-tin-zinc-oxide thin-film transistor with hexamethyldisilazane passivation. ACS Appl. Electron. Mater. 6 (4), 2442–2448. https://doi.org/10.1021/acsaelm.4c00100 (2024).

Chung, H. J., Kim, D. H. & Kim, B. K. Hysteresis characteristics in low temperature poly-Si thin film transistors. J. Inf. Disp. 6 (4), 6–10. https://doi.org/10.1080/15980316.2005.9651984 (2010).

Kim, B. K., Kim, O., Chung, H. J., Chang, J. W. & Ha, Y. M. Recoverable residual image induced by hysteresis of thin film transistors in active matrix organic light emitting diode displays. Jpn J. Appl. Phys. 43, L482–L485. https://doi.org/10.1143/JJAP.43.L482 (2004).

Hwang, H. W. et al. Analysis of recoverable residual image characteristics of flexible organic light-emitting diode displays using polyimide substrates. IEEE Electron. Device Lett. 40 (7), 1108–1111. https://doi.org/10.1109/LED.2019.2914142 (2019).

Jeon, C. H., Um, J. G., Mativenga, M. & Jang, J. Fast threshold voltage compensation AMOLED pixel circuit using secondary gate effect of dual gate a-IGZO TFTs, IEEE Electron Device Lett. 37(11), 1450–1453. https://doi.org/10.1109/LED.2016.2613400 (2016).

Kim, J. C. et al. A novel LTPO AMOLED pixel circuit and driving scheme for variable refresh rate. J. Inf. Disp. 24 (4), 283–298. https://doi.org/10.1080/15980316.2023.2213848 (2023).

Lee, J. H., Park, S. G., Han, S. M., Han, M. K. & Park, K. C. New PMOS LTPS–TFT pixel for AMOLED to suppress the hysteresis effect on OLED current by employing a reset voltage driving. Solid-State Electron. 52 (3), 462–466. https://doi.org/10.1016/j.sse.2007.10.030 (2008).

Zhou, Z. H. et al. A physical charge-based model for transient response of metal oxide thin-film transistors considering relaxation of trap states. IEEE Trans. Electron. Devices 71 (12), 7524–7529. https://doi.org/10.1109/TED.2024.3484350 (2024).

Cho, I. T., Lee, J. M., Lee, J. H. & Kwon, H. I. Charge trapping and detrapping characteristics in amorphous InGaZnO TFTs under static and dynamic stresses. Semicond. Sci. Technol. 24 (1), 015013. https://doi.org/10.1088/0268-1242/24/1/015013 (2008).

Kim, S. J. et al. Effect of charge trapping/detrapping on threshold voltage shift of IGZO TFTs under AC bias stress. Electrochem. Solid-State Lett. 15 (4), H108. https://doi.org/10.1149/2.026204esl (2012).

Kim, T., Park, S. & Jeon, S. Fast and slow transient charging of oxide semiconductor transistors. Sci. Rep. 7 (1), 11850. https://doi.org/10.1038/s41598-017-12155-3 (2017).

Acknowledgements

This work was supported by the LG Display Co., Ltd.

Author information

Authors and Affiliations

Contributions

D.S.Sim organized the data, drew figures, and wrote the main manuscript text. All authors reviewed the results and implications and commented on the manuscript at all stages. The project was guided by H.J.Kim (corresponding author).

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Sim, D.S., Jung, S., Kim, B.C. et al. Improvement of flicker phenomenon at low frequencies in AMOLED displays by applying compensation scheme of variable reset voltage. Sci Rep 15, 12181 (2025). https://doi.org/10.1038/s41598-025-96847-1

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-025-96847-1